# A Random Access Photodiode Array for Intelligent Image Capture

Orly Yadid-Pecht, Ran Ginosar, Member, IEEE, and Yosi Shacham Diamand

Abstract—A novel chip implementing random scan was designed, fabricated, and tested. The chip covers the basic requirements for random access and separation between the sampling and reading processes. In this way, a repeated reading of any pixel at any time can take place. The chip includes an 80  $\times$  80 matrix of basic cells. Each cell consists of two stages: The first is based on a switch, whereas the second includes a buffer. The chip was fabricated in a 3-µm CMOS process. It was found to operate functionally. However, the use of a standard process gave rise to the crosstalk phenomenon, which has yet to be overcome.

#### I. Introduction

TWO APPROACHES are typically used for imaging electro-optical systems. These two methods differ by the type of detector element used. The first is based on the detection of light intensity at every pixel (picture element) in the image plane by an electron beam (the "flying spot" technique [1]). The second method is based on the presence of detector elements in every pixel, arranged in a two-dimensional (2D) array.

Detector array technologies have been developed with the advance of microelectronics and very large scale integration (VLSI). The solid-state imagers that are discussed here use the electrooptical properties of semiconductor materials for sensing electromagnetic radiation. Signal processing units can be attached to the detectors at the focal plane of the optical system. The output signals are typically read sequentially, using electronic scanning techniques. The 2D array is an expansion of the linear array concept, which by itself is the expansion of the single detector element.

Charge transfer techniques are the most common method used by 2D imaging arrays. In this approach, photo-generated charge is collected and transferred in a predetermined way. The two common charge transfer technologies used are charge-coupled device (CCD), introduced by Boyle and Smith [2], and charge injection devices (CID) proposed by Burke and Michon [3]. The advantages and disadvantages of these methods are summarized, for example, by Barbe [4].

In addition to the charge transfer devices, other concepts for discrete optical detector arrays have been imple-

Manuscript received May 18, 1990; revised November 2, 1990. The review of this paper was arranged by Associate Editor W. F. Kosonocky.

The authors are with the Department of Electrical Engineering, Technion—Isreal Institute of Technology, Haifa, Isreal.

IEEE Log Number 9144390.

mented. One common concept is an array of light-sensitive p-n semiconductor junctions, which are also called photodiodes.

The main advantage of the photodiode array over the charge-transfer devices in the simplicity of fabrication—it does not require special technology; a conventional MOS process is sufficient. However, in order to obtain better sensors, special "tailored" processes were developed. This will be further discussed in the conclusions section. Another advantage of the photodiode array is that random scan can be easily implemented as each pixel can be accessed separately and independently, unlike in charge transfer devices.

The main goal in this design is the availability of random access. Every pixel can be reached independently by this approach. Although the array acquires all the information, part of it might not be read at all. On the other hand, there might be parts of the information that will be read more than once. This design, with the availability of the random access concept, has its use in intelligent scan systems [5]. It imitates the eye operation in which there is a foveating system that scans the picture with the help of the eye ball. The result is a nonuniform scanned picture. The sensor described here allows selective data acquisition.

The design includes an addressed array. Each cell consists of light detection, information holding, and reading out. In order to decouple between the light detection and the algorithms of computer vision that decide which pixels to read, and in order to prevent interdependence between them, the processes are separated, i.e., the light sensing is periodical but reading can take place at any time. Even more, the algorithm is allowed to read a pixel more than once (before it is sampled again).

Several alternatives for designing the basic cell were considered, and the best alternative was chosen for the final design. A chip of  $80 \times 80$  cells and a test chip were designed, fabricated, and tested. They were found to work functionally. However, the use of a standard process (that is mainly used for digital use) gave rise to the crosstalk phenomenon.

Section II describes the chip overall design concepts, whereas Section III deals with the unit cell design concepts. Section IV describes the alternative basic cell configurations, and Section V describes the basic cell layout. Section VI describes the test chip. In Section VII, we ana-

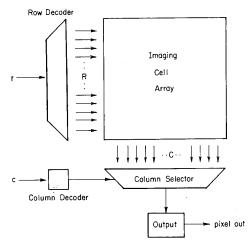

Fig. 1. General chip design.

lyze the chip expected performance, and Section VIII describes the experimental performance. Section IX concludes the paper.

#### II. CHIP DESIGN CONCEPTS

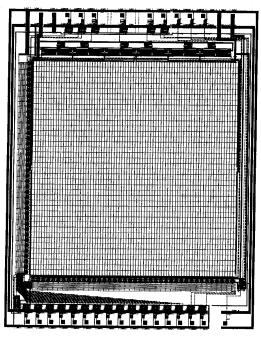

The chip architecture is similar to that of random access memories-RAM's. The advantage of this architecture is that the location of important video data can be immediately accessed and processed without wasting time on nonrelevant video data. The overall design is shown in Fig. 1. A 2D array of R rows and C columns of imaging cells occupies most of the chip area. Readout is accomplished by addressing the row and column of a particular pixel. The row is accessed by a row decoder, which selects one of the R output lines. Simultaneously, the columns carry the contents of the Rth row. Each column bus is connected to the single output bus through the column selector, which consists of switches (pass transistors) controlled by a column decoder. The output bus is further connected to an output amplifier that transfers the analog information out.

The two basic design principles in this chip design are

- a) enabling random access to each pixel

- b) separating the sensing section from the readout in such a way that each pixel can be read at any time during the integration period. Multiple readings of the same pixel are possible. This second principle demands a special cell design, which is discussed in the following section.

One of the design goals was to achieve maximum speed in minimum area. However, a scanning circuit for each row and each column is provided to enable random scan. The integration period was chosen to be uniform for all pixels in order to simplify the individual pixel design. An  $80\times80$  matrix in a  $7.9\times9.2$ -mm chip was designed. The matrix area fills around 65% of the chip area.

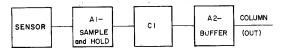

Fig. 2. Basic cell-block diagram.

# III. UNIT CELL DESIGN CONCEPTS

The basic cell organization is shown in Fig. 2. The input signal to each pixel is the light intensity at that location. It is transduced by a diode (the sensor) and its associated circuits to an analog voltage at the output. The sensing is done via a reverse-biased photodiode, which is reset periodically to a fixed bias. The diode collects the photogenerated electrons and discharges in proportion to the integration period and the diode photocurrent. The cell includes a sample and hold circuit (S&H, A1), which forms the first stage, a memory capacitor (C1), and a second stage (A2). The design realizes the required separation between the sensing and reading processes. The memory capacitor C1 will keep the sampled value for additional readings in the same integration period.

The pixel size should be minimized in order to achieve higher resolution. Therefore only n-type channel transistors were used in each cell, although the chip was fabricated using CMOS technology. In general, the cell operation consists of three parts: a) sensing, b) sampling, and c) reading.

After the desired integration period, the signal is sampled and transferred to the memory capacitor. The voltage on the capacitor depends on the transfer function of the sample unit A1 (see Fig. 2). A1 can be either a voltage follower buffer or a switch that transfers some of the charge stored in the photodiode depletion capacitance into the memory capacitor. In the latter case, the capacitor should be precharged to a starting voltage before the sampling.

This design allows the separation of the reading from the sensing. The reading may occur several times during the sensing of a new value, whereas the sample and reset switches are off. For reading, the row-select switch closes, and the voltage is transferred to the column bus. The voltage depends on the transfer function of A1 (see Fig. 2). Reading will be accomplished by closing the column-select switch to pass the column value to the output.

The alternatives for A1 and A2 will be further discussed in the following section.

# IV. ALTERNATIVE BASIC CELL CONFIGURATIONS

Several configurations were considered for the basic cell, differing in the implementation of the A1 and A2 units. The first was a pure sample and hold circuit with switches only. Other possibilities included using one or two buffers separating the different parts of the cell.

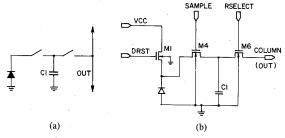

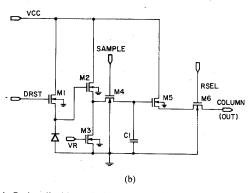

Fig. 3(a) shows a schematic description of the basic sample and hold circuit. An electrical description is given in Fig. 3(b) Transistor M1 precharges the diode at the begining of every integration period. Transistor M4 with

Fig. 3. Basic cell with MOS switches only: (a) Schematic description; (b) electrical description.

Fig. 4. Basic cell with two buffers: (a) Schematic description; (b) electrical description.

the sample pulse accomplishes the sampling, whereas transistor M6 with the row select (RSel) pulse enables the reading of the C1 capacitor voltage. This implementation achieved the smallest area. However, in order to attain multiple readings, the value on the capacitor should stay constant between the readings, and therefore, this implementation is unsatisfactory.

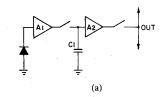

The use of buffers enables simple application of multiple readings. There are two possible configurations:

- 1) With two buffers: In this approach there is one buffer between the photodiode and the capacitor (A1) and another buffer between the capacitor and the column bus (A2; see Fig. 4).

- 2) With one buffer: In this design, A1 is implied with a pass transistor so that charge sharing takes place between the diode and the capacitor, and a buffer exists only between the capacitor and the column (A2; see Fig. 5).

In both options, there is a buffer between the capacitor and the column. It can be implemented as a source fol-

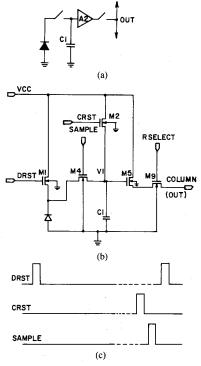

Fig. 5. Basic cell electrical description: (a) Schematic description; (b) electrical description; (c) signal timing: Diode is reset (DRST) at the beginning of the integration interval. At the end, the memory capacitor is reset (CRST) followed by sample. Subsequently, the diode is reset again.

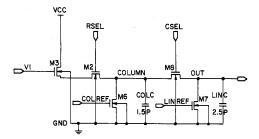

Fig. 6. Electric description of the output to the column and video lines.

lower, using two transistors. Transistor M2, which serves as a current source and can be either part of the basic cell or shared among all cells of the column. The external current source was preferred for two reasons: It saves area, and it can be made stronger to affect faster response. Fig. 6 shows the way out of the basic cell (from the capacitor) that is similar for both configurations using buffers. M3 is the upper part of the cell output buffer A2. M6 is the corresponding current source, which is shared for the column. M2 is the RSel transistor that is a part of each cell, whereas M8 is the column select (CSel) transistor, which connects the column transistors to the output amplifier.

# A. Two Buffers Alternative

Fig. 4 illustrates the use of two buffers in the basic cell. Transistor M1 precharges the junction capacitance of the

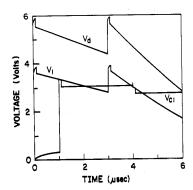

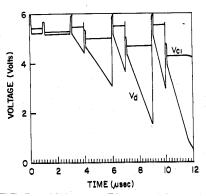

Fig. 7. Simulation of the first stage with a buffer:  $V_d$  is the simulated diode voltage,  $V_1$  is the simulated voltage after the source follower, and  $V_{C1}$  is the simulated voltage on capacitor C1.

photodiode. Transistors M2 and M3 constitute the source follower that transfers the diode voltage to the memory capacitor C1. The signal is decreased to about 80% of its value because of the bulk effect. Following the source follower, M4 is the signal sampling switch. M5 is the upper part of the second stage buffer; recall that the current source of this buffer is shared on the column.

Simulation results of this design are shown in Fig. 7. At t=0, the diode is reset (the capacitance coupling is evident). At  $t=1~\mu s$ , sampling is performed for about 100 ns starting at  $t=1~\mu s$ . Following the switch opening, the voltage on the capacitor  $V_{C1}$  remains stable till the next sampling (at  $t=3~\mu s$ ), whereas the diode voltage  $V_d$  and the voltage of the first source follower  $V_1$  continue to decrease due to photodischarge. At  $t=3~\mu s$ , the diode is reset again. The simulated photocurrent was higher during the second integration interval ( $t=3~through~6~\mu s$ ) than for the first ( $t=0~through~3~\mu s$ ), as can be noted from the two  $V_d$  shapes. Note that the time and current scales are compressed to enhance transient responses.

#### B. One Buffer Alternative

Fig. 5 showed the basic cell design with one buffer only. The transistors perform the same role as in the two-buffer configuration, except that here, there is no first stage buffer, and a transistor for precharging the capacitor (M2) is needed. Fig. 8 shows the simulation results for this design, with integration intervals of 3  $\mu$ s similar to Fig. 7. At  $t = (3 \cdot n) \mu$ s,  $n = 0, 1, \cdots$ , the diode and capacitor are precharged. This takes about 50 ns when minimum size transistors of 3- $\mu$ m CMOS are employed. At  $t = (3n + 1) \mu$ s, sampling is done, and the capacitor voltage  $V_{C1}$  changes in proportion to the diodes voltage  $V_{d}$ . Samping takes about 10 ns. Note again that the discharging current was changed in this simulation from one integration interval to another.

# C. The Preferred Configuration

Table I shows a comparison of some parameters of the alternative configurations. SNR is discussed in Section

Fig. 8. Simulation of the first stage with a pass transistor:  $V_d$  is the simulated diode voltage, and  $V_{C1}$  is the simulated voltage on capacitor C1.

# TABLE I COMPARING THREE ALTERNATIVE CONFIGURATIONS

|                                                                         | Basic S & H | S & H With<br>Two Buffers | S & H With<br>One Buffer |

|-------------------------------------------------------------------------|-------------|---------------------------|--------------------------|

| Area (no. of transistors) Multiple readings Signal-to-noise ratio (SNR) | small (4)   | large (6)                 | medium (5)               |

|                                                                         | destructive | nondestructive            | nondestructive           |

|                                                                         | bad         | good                      | good                     |

VII-B below. We have chosen to use the single buffer configuration as shown in Fig. 5. This circuit was preferred because of area considerations and nondestructive multiple readings.

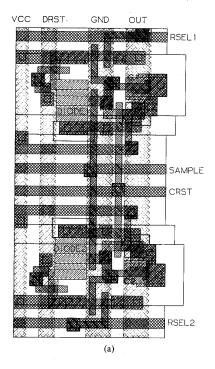

## V. BASIC CELL LAYOUT

The basic layout unit is shown in Fig. 9(a). It includes two cells in which the sample, the capacitor reset (CRST), and the diode reset (DRST) lines are shared. Similarly, the supply and output lines are shared vertically between all the cells in a column. The DRST line was laid vertically to maintain a square shape for each cell. The width of each cell is 48  $\lambda$ , and the length varies between 47 and 49  $\lambda$ . The array distortion caused by this is negligible. The fill factor is around 6%, and the diode size is 10  $\times$  13  $\lambda$ . In the current design  $\lambda = 1.5~\mu m$ . The basic cell pass transistor size was chooen to be the minimum size available in the given technology.

The diode is an n<sup>+</sup>-p source/drain diode inside a p-well with total capacitance of about 115 fF at zero bias. This capacitance decreases as the diode voltage increases, and assuming 0-5-V backward bias, its average is  $\sim 50$  fF. The memory capacitor C1 was designed for the same order of magnitude as the diode capacitance. It is implemented by a MOS transistor with a source and drain shorted. This capacitance  $C1 \sim 50$  fF consists of the gate oxide capacitance, the parasitic capacitors of the transistors source/drain diodes, and the capacitance between the polysilicon and metal lines.

The vertical lines were made of the second metal level. All the active areas, except the photodiode, were covered by metal to prevent light penetration to other diodes. This

Fig. 9. Layout design: (a) Basic layout unit; (b) overall chip layout.

light may cause photoinduced current in other circuit nodes. Those currents may interfere with the unit cell operation and appear as crosstalk in other cells, as is further discussed in Section VIII-C. The overall chip layout design is shown in Fig. 9(b).

# VI. TEST CHIP DESIGN

In addition to the  $80 \times 80$  array chip, we have also designed and fabricated a smaller test chip. The test chip is devised for measuring and characterizing the various components. This chip includes the following:

- discrete components, such as transistors, input, and output buffers

- 2) matrices: an 8 × 8 matrix, a 4 × 4 matrix with the two-buffer alternative design, and 4 × 4 matrix with variations on the part of the diode exposed to light

- big cells, which are 25 times bigger than the regular cells, with variations on the capacitor size.

- a special purpose cell in which the current in the diode is controlled by an external voltage source.

The big cells consist of the same basic cell design but are five times larger in each dimension. The capacitor, the diode, and the transistors are bigger so that small dimension effects will be less pronounced. Both the capacitor and the photodiode are estimated as 1 pF.

The current source test cell enables external control over the diode current. The diode is also protected from light; therefore, no photocurrent should be generated.

# VII. PERFORMANCE ANALYSIS

# A. Diode and Capacitor Voltage

The diode operates periodically; it is precharged to a starting voltage and discharges relative to the light intensity. When the diode is reverse biased, a depletion layer forms, with charge areal density  $Q = q \cdot N \cdot x_d$ , where

- q electron charge

- N density of dopant atoms in a unit volume

- $x_d$  depletion layer depth.

The depletion layer collapses with light and thermal generation, and the time derivative of its charge is equal to the generation currents

$$\frac{dQ}{dt} = -qN \frac{dX_d}{dt} = -\eta J_{ph} - q \frac{n_i}{2\tau} \cdot x_d \tag{1}$$

where

- η quantum efficiency

- $J_{ph}$  light current areal density

- $n_i$  density of intrinsic electrons

- $\tau$  lifetime of the minority carriers.

Assuming the dark current is negligible, the secondorder approximation of the voltage as a function of time is given by

$$V = V_0 - \frac{\eta J_{ph} \cdot t}{\epsilon \epsilon_0} X_{\text{max}} + \frac{qN}{2\epsilon \epsilon_0} \left( \frac{\eta J_{ph} t}{qN} \right)^2.$$

(2)

The above expression indicates that for a linear voltage function of time the integration period should be shorter than  $2qNX_{\text{max}}/\eta J_{ph}$ .

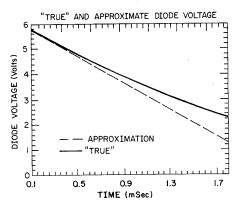

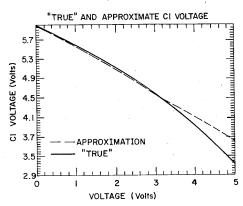

Fig. 10. Calculated "true" and approximate diode voltage.

Fig. 10 shows the calculated voltage as obtained by (2) in comparison with the linear approximation. The linear approximation is close for short integration periods, whereas the distortion gets larger for longer integration. A look-up table (L.U.T) can be implemented in ROM in order to achieve a more linear transfer function.

Note that a step junction was assumed. With an assumption of a linear junction, different results will be obtained, as the basic relation between the voltage and the depletion layer width will be of  $x_d^3$  [6] and not square, as was set out in the above calculation.

At the sampling, the diode shares its charge with the capacitor. Here too, there is a nonlinear relation, as the junction capacitance changes by

$$C_{j}(V) = \frac{C_{j}(0)}{\left(1 + \frac{V_{a}}{V_{b}}\right)^{1/2}}$$

(3)

for a step junction where

$C_j(0)$  junction's capacitance with no applied voltage  $V_a$  diode applied voltage

$V_b$  "built-in" junction voltage.

Fig. 11 shows the final capacitance calculated voltage and the approximate voltage taken for an average capacitance of the diode. Again, a L.U.T. can fix this distortion.

#### B. Noise

For SNR calculation, the uncertainty is calculated in number of electrons. Table II summarizes the different calculated noise sources in the circuit [7]. The first source  $(\bar{n}_{SN1}^2)^{1/2}$  is the uncertainty in number of electrons caused by the photocurrent shot noise.  $(\bar{n}_{SN2}^2)^{1/2}$  is the uncertainty due to the dark current shot noise.  $(\bar{n}_{DRST}^2)^{1/2}$  is the uncertainty due to the thermal noise of the reset switch (KTC noise).  $(\bar{n}_{MD}^2)^{1/2}$  refers to the uncertainty caused by charge injection to the diode (switching noise).  $(\bar{n}_{CRST}^2)^{1/2}$  is caused by the capacitor reset.  $(\bar{n}_{sample}^2)^{1/2}$  is caused by the sampling (KTC).  $(\bar{n}_{MC}^2)^{1/2}$  is the uncertainty caused

Fig. 11. "True" and approximate capacitor final voltage.

TABLE II Noise Sources Summary

| Noise<br>Source                          | Description                                     | Quantitative Estimation (in electronic charges) |

|------------------------------------------|-------------------------------------------------|-------------------------------------------------|

| $(\overline{n}_{SN1}^2)^{1/2}$           | Photocurrent uncertainty                        | 1060 [ele]                                      |

| $(\overline{n}_{SN2}^2)^{1/2}$           | Dark current uncertainty                        | 34 [ele]                                        |

| $(\overline{n}_{DRST}^2)^{1/2}$          | Diode reset uncertainty (KTC)                   | 136 [ele]                                       |

| $(\overline{n}_{MD}^2)^{1/2}$            | Charge injection uncertainty (at the diode)     | 118 [ele]                                       |

| $(\overline{n}_{CRST}^2)^{1/2}$          | Capacitor's reset uncertainty (KTC)             | 96 [ele]                                        |

| $(\overline{n}_{\text{sample}}^2)^{1/2}$ | Reading uncertainty (sample)                    | 65 [ele]                                        |

| $(\overline{n}_{MC}^2)^{1/2}$            | Charge injection uncertainty (at the capacitor) | 118 [ele]                                       |

by the charge injection to the capacitor. The source follower noise is negligible. Two noise electrons are contributed by the nMOS buffer, and the output buffer (in pMOS) contribution is less than one. The following calculation is correct as long as charge conservation is valid, i.e., for the path that starts with the diode and ends at the capacitor. The sample noise and the noise source in the upper MOS transistor of the buffer can also be added, without violating the charge conservation assumption. The total noise is calculated as

$$\overline{N}_{n}^{2} = (\overline{n}_{SN1}^{2} + \overline{n}_{SN2}^{2} + \overline{n}_{DRST}^{2} + \overline{n}_{MD}^{2} + \overline{n}_{CRST}^{2} + \overline{n}_{MC}^{2})A_{1}^{2} + \overline{n}_{sample}^{2} + \overline{n}_{MOS}^{2}$$

(4)

where  $A_1$  is the transfer function from the diode to the capacitor (see Fig. 2). The total uncertainty is obtained by  $\sqrt{\overline{N}_n^2} = 547$ .

For the SNR calculation, the maximum charge signal at the output is divided by the noise signal. The maximum charge is maximum voltage (5 V) formed on 41 fF (capacitor at 5 V), i.e., 512 500 electrons at the output. Thus SNR is about 60 dB (1000).

#### VIII. EXPERIMENTAL RESULTS

The sensor and the test chips were both fabricated in a  $3-\mu m$  CMOS p-well process. Here, we summarize the measurements.

# A. Performance of the Sampling Array

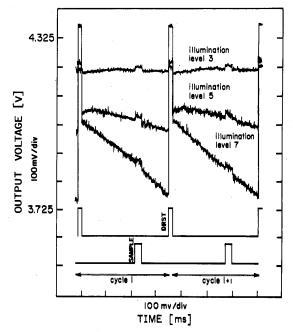

As described earlier, the diode discharges in proportion to the light intensity and the integration period. During the sampling phase, the diode charge is shared with the capacitor. The "sampled" charge on the capacitor should remain constant till the next sampling.

Fig. 12 shows sampling at different light levels. Note that the value of the sampled voltage depends on light intensity properly. However, the tests show that the unwanted memory capacitor discharge due to light is much stronger than predicted by the "dark current" leakage process. We would expect the sampled voltage on the capacitor to remain constant. However, it clearly discharges: If the light is stronger, the discharge is faster. Recalling that the capacitor is actually a combination of several capacitors in which diffusion capacitance contributes around 30%, this can be due to the carriers generated under the exposed diode having a lifetime that is long enough to diffuse and discharge the capacitor even though it is protected from light. The conclusion section discusses the avoidance of this phenomenon.

#### B. Crosstalk

The effect described above is also referred to as crosstalk, which describes photocarriers that affect nodes that are far from the original illumination [8].

Crosstalk arises from both optical and electrical reasons. The optical crosstalk was investigated by illuminating a covered diode and measuring the response as a function of distance from the original illumination site. The light spot diameter was about 200  $\mu$ m, and it was smaller than the big diode size. Optical crosstalk was observed. i.e., the covered diode cell and the cells beside it responded to the lights. The covered cell was designed to check the diode operation with an external voltage controlling the current. Change in the external voltage showed different discharge rates, but even with the external voltage disconnected, different light levels caused different discharge rates. This means that part of the crosstalk is caused by light that manages to "travel" laterally along the chip. The cause might be the waveguide formed by the SiO<sub>2</sub> layer.

The main contribution to the crosstalk is electrical: the discharge of near cells due to the long lifetime minority carriers. This was further checked as is explained in the following.

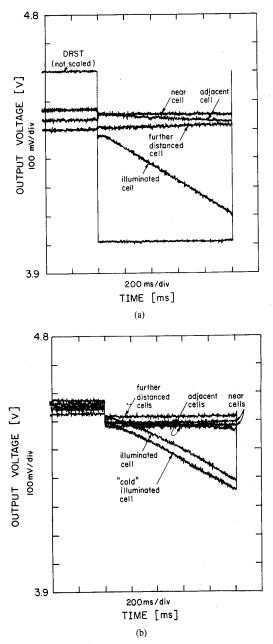

# C. The Effect of Cooling

The minority carriers lifetime dependence on temperature in silicon at the 270–350 K range is approximately linear [9]. The accurate function is complicated, and attaining a theoretical explanation of the empirical tests depends on the assumption of trap cross section ( $\sigma$ ) and depth side in the forbidden gap that change with temperature.

The chip was cooled (using fluid Freon) to about  $-20^{\circ}-40^{\circ}$ C (roughly estimated). By comparing the results in the big test cells before and after cooling, it was found

Fig. 12. Sampling different illumination levels.

that after cooling, a stronger discharge occurred in the illuminated cell, while the discharge in the adjacent cells became negligible (see Fig. 13). On the other hand, at room temperature, the adjacent cells are strongly influenced by the illuminated diode. This agrees with common assumption that if the temperature is lower, the diffusion length is shorter [9].

## D. Remarks

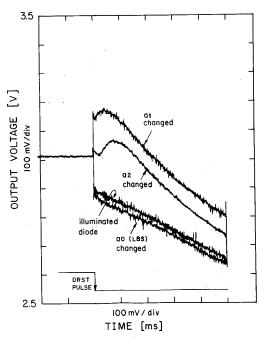

All the nodes in the circuit affect the output voltage from each cell. Therefore, full simulation of the chip behavior is very complicated as each node in the sensor matrix and at the peripheral circuits is affected by the light because of the carriers long lifetime. The experimentally measured response of a cell in the sensor matrix and its neighbors is shown in Fig. 14. The response following the change in a0 (least significant bit) (LSB) is denoted by "a0 changed." Correspondingly, the response followed by the change of a1 (second LSB) and of a2 are shown. Using this standard process, therefore, makes separation between the cells mandatory. It can be achieved by surrounding each diode with a "guard ring" or putting each diode in a separate well.

### IX. Conclusions

We have described the design and test of a randomaccess photodiode array sensor. It has been planned for intelligent scan applications [5]. The chip fulfilled the basic requirements for random access and independent sampling and reading processes.

The chip architecture resembles random access memory (RAM) design. It consists of R rows and C columns

Fig. 13. Test results: (a) at room temperature; (b) after cooling.

of cells, which can be accessed independently. Each cell consists of a photodiode, a memory capacitor, and switching transistors. Several alternative designs of the basic cell were tested, differing with the implementation of the connecting blocks, i.e., with or without buffers. The chosen alternative has a buffer at the second stage, in which the current source transistor is shared between all the column transistors.

The alternative designs were simulated, and the results were shown. A novel chip of 80 × 80 cells with the preferred configuration was fabricated and tested. With it, a

Fig. 14. Measured results in close small cells (at the sensor matrix).

test chip for checking the alternative designs, measuring, and characterizing the chip different components was fabricated and tested as well.

The chip was found to operate functionally (see Figs. 12-14). However, the results point to drawbacks in the design. The crosstalk was found to be the most problematical and has to be overcome. This phenomenon has been encountered before, and several technological solutions can be found in the literature [8], [10], [11].

However, if one still wants to use a standard CMOS process for the imager, future versions will require more area per cell to protect from crosstalk. For instance, fabricating each photodiode in a different well, or inserting guard rings between the diodes, are two possible solutions aimed at isolating the sensors from each other.

#### ACKNOWLEDGMENT

Thanks to Prof. Bar-Lev for reviewing this article and giving helpful comments. Thanks also to Dr. D. Lubzens and T. Blum for their continuous help and assistance during the work.

#### REFERENCES

- [1] D. H. Ballard and C. M. Brown, Computer Vision. Cliffs, NJ: Prentice Hall, 1982.

- W. Boyle and G. Smith, "Charge coupled semiconductor devices," Bell Syst. Tech. J., vol. 49, pp. 587-593, 1970.

- [3] H. K. Burke and G. J. Michon, "Charge injection imaging: Operation techniques and performance characteristics," IEEE J. Solid State Circuits, vol. SC-11, pp. 121-127, 1976.

- [4] D. F. Barbe, "Imaging devices using the charge coupled concept," Proc. IEEE, vol. 63, no. 1, pp. 38-66, Jan. 1975.

[5] Y. Y. Zeevi and R. Ginosar, "Neural networks for foveating visual

- systems," in R. Eckmiller (Ed.), Advanced Neural Computers. New York: Elsevier, 1990.

- [6] A. Bar-Lev, Semiconductors and Electronic Devices. Haifa, Israel: Michlol, 1976.

- [7] O. Yadid-Pecht, "An imaging system with random access," M.Sc. thesis, Technion-I.I.T., Haifa, Isreal, 1990.

- [8] J. D. E. Beynon and D. R. Lamb, Charge-Coupled Devices and Their Applications. London: McGraw-Hill, 1980.

- [9] P. G. Wilson, "Recombination in silicon p-π-n diodes," Solid-State Electron., vol. 10, pp. 145–154, 1975.

- [10] T. Yamada et al., "A 3648 CCD linear image sensor," in IEDM 82, pp. 320-323, 1982.

- [11] Y. Ishihara et al., "Interline CCD image sensor with an antiblooming structure," *IEEE Trans. Electron Devices*, vol. ED-31, no. 1, pp. 83-88, 1984.

Orly Yadid-Pecht received the B.Sc. and M.Sc. degree in electrical engineering from the Technion, Israel Institute of Technology in 1983 and 1990, respectively.

She is now working towards the Ph.D. degree in biomedical engineering in the Technion.

Ran Ginosar (M'82) received the B.Sc. degree in electrical engineering and computer science Summa cum Laude from the Technion, Israel Institute of Technology, in 1978 and the Ph.D. from Princeton University, Princeton, NJ, in 1982.

After conducting research at Bell Laboratories for one year, he joined the faculty of Electrical Engineering at the Technion. His areas of interest include the architecture of VLSI systems and of integrated sensor/processor systems for advanced electronic imaging.

Yosi Shacham-Diamand was born in Israel, on June 26, 1953. He received the B.Sc., M.Sc., and D.Sc. degrees in electrical engineering from the Technion-Israel Institute of Technology, Haifa, Israel, in 1977, 1979, and 1983, respectively.

From 1983 to 1986, he was a Visiting Research Associate at the Electronics Research Laboratories of the University of California, Berkeley. In 1986, he also held the position of a Visiting Lecturer at the Department of Electrical Engineering and Computer Science at the University of California, Berkeley. In 1986, he joined the Technion as a Senior Lecturer in the Department of Electrical Engineering. At present, he is a Visiting Assistant Professor in the Electrical Engineering Department at Cornell University, Ithaca, NY. He is currently involved in research on VLSI technology, multi-alyer interconnection schemes, microlithography, and analog CMOS technology.